Product Summary

The OR2C04A-2T144 is a SRAM-based FPGA. The OR2C04A-2T144 is an enhanced version of the ATT2C/2T architecture. The latest ORCA series includes patented architectural enhancements that make functions faster and easier to design while conserving the use of PLCs and routing resources. The Series 2 device can be used as drop-in replacements for the ATT2Cxx/ATT2Txx series, respectively, and the device is also bit stream compatible with each other.

Parametrics

OR2C04A-2T144 absolute maximum ratings: (1)Storage Temperature, Tstg: -65 to 150℃; (2)Supply Voltage with Respect to Ground, VDD: -0.5 to 7.0 V; (3)VDD5 Supply Voltage with Respect to Ground (OR2TxxA), VDD5: VDD to 7.0 V; (4)Input Signal with Respect to Ground OR2TxxA only: -0.5 to VDD + 0.3V; -0.5 to VDD5 + 0.3V; (5)Signal Applied to High-impedance Output OR2TxxA only: -0.5 to VDD + 0.3V; -0.5 to VDD5 + 0.3V; (6)Maximum Soldering Temperature: 260℃.

Features

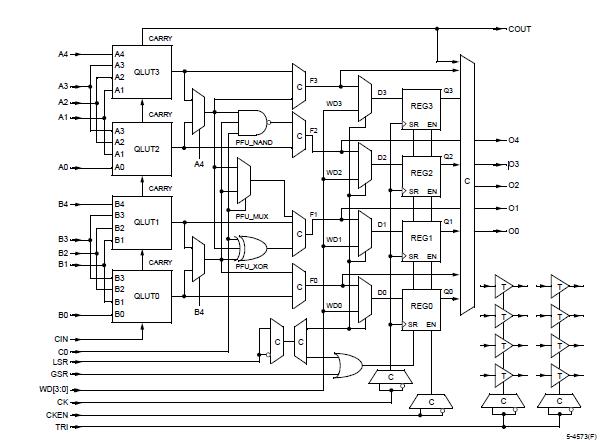

OR2C04A-2T144 features: (1)High-performance, cost-effective, low-power 0.35 μm CMOS technology (OR2CxxA), 0.3 μm CMOS technology (OR2TxxA), and 0.25 μm CMOS technology (OR2TxxB), (four-input look-up table (LUT) delay less than 1.0 ns with -8 speed grade); (2)High density (up to 43,200 usable, logic-only gates; or 99,400 gates including RAM); (3)Up to 480 user I/Os (OR2TxxA and OR2TxxB I/Os are 5 V tolerant to allow interconnection to both 3.3 V and 5 V devices, selectable on a per-pin basis); (4)Four 16-bit look-up tables and four latches/flip-flops per PFU, nibble-oriented for implementing 4-, 8-, 16-, and/or 32-bit (or wider) bus structures; (5)Eight 3-state buffers per PFU for on-chip bus structures; (6)Fast, on-chip user SRAM has features to simplify RAM design and increase RAM speed: Asynchronous single port: 64 bits/PFU; Synchronous single port: 64 bits/PFU; Synchronous dual port: 32 bits/PFU; (7)Improved ability to combine PFUs to create larger RAM structures using write-port enable and 3-state buffers; (8)Fast, dense multipliers can be created with the multiplier mode (4 x 1 multiplier/PFU): 8 x 8 multiplier requires only 16 PFUs; 30% increase in speed; (9)Flip-flop/latch options to allow programmable priority of synchronous set/reset vs. clock enable; (10)Enhanced cascadable nibble-wide data path capabilities for adders, subtractors, counters, multipliers, and comparators including internal fast-carry operation.

Diagrams

(Hong Kong)

(Hong Kong)