Product Summary

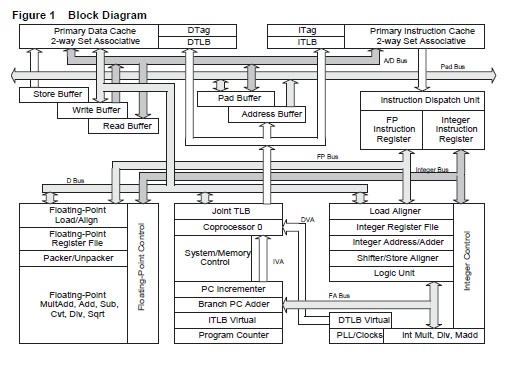

The RM5261A-400H is a microprocessor with 64-bit system bus. The RM5261A-400H offers a high-level of integration targeted at high-performance embedded applications. The key elements of the RM5261A-400H are briefly described below. The RM5261A-400H has an asymmetric superscalar dispatch unit which allows it to issue an integer instruction and a floating-point computation instruction simultaneously. Integer instructions include alu, branch, load/store, and floating-point load/store, while floating-point computation instructions include floating-point add, subtract, combined multiply-add, and convert.

Parametrics

RM5261A-400H absolute maximum ratings: (1)VTERM Terminal Voltage with respect to Vss: –0.52 to +3.9 V; (2)TCASE Operating Temperature Commercial: 0 to +85 °C, Industrial: –45 to +85 °C; (3)TSTG Storage Temperature: –55 to +125 °C; (4)IIN DC Input Current: ±203 mA; (5)IOUT DC Output Current: ±204 mA.

Features

RM5261A-400H features: (1)Dual Issue superscalar microprocessor; (2)250, 300, and 350 MHz operating frequencies; (3)Up to 420 Dhrystone 2.1 MIPS; (4)High-performance system interface; (5)IEEE 1149.1 JTAG boundary scan; (6)Integrated on-chip caches; (7)32 KB instruction and 32 KB data — 2 way set associative; (8)Per set locking; (9)Virtually indexed, physically tagged; (10)Write-back and write-through on a per page basis; (11)Pipeline restart on first doubleword for data cache misses; (12)Integrated memory management unit; (13)Fully associative joint TLB (shared by I and D translations); (14)Single cycle repeat rate for single-precision combined multiply-add operation; (15)MIPS IV instruction set; (16)Conditional moves to reduce branch frequency; (17)Index address modes (register + register); (18)Embedded application enhancements; (19)I and D cache locking by set; (20)Optional dedicated exception vector for interrupts; (21)Fully static 0.18 micron CMOS design with power down logic; (22)208-pin QFP package.

Diagrams

(Hong Kong)

(Hong Kong)