Product Summary

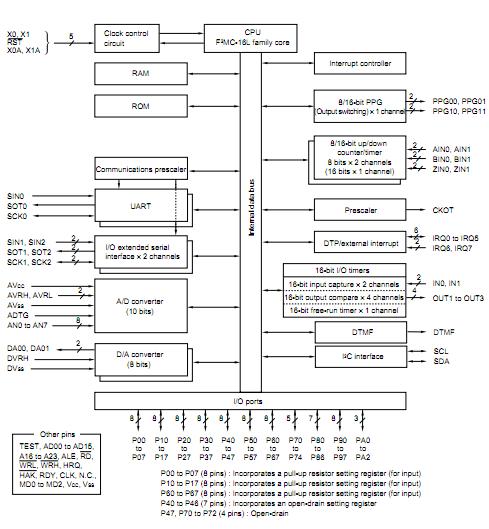

The MB90652APFV-G-195-BND is a 16-bit microcontroller designed for high speed real-time processing in consumer product applications such as controlling celluar phones, CD-ROMs, or VTRs. Based on the F2MC*1-16L CPU core, an F2MC-16L is used as the CPU. The MB90652APFV-G-195-BND includes high-level language-support instructions and robust task switching instructions, and additional addressing modes. In order to reduce the consumption current, dual-clock (main/sub) is used. Furthermore, low consumption power supply is achieved by using stop mode, sleep mode, watch mode, pseudo-watch mode, CPU intermittent operation mode.

Parametrics

MB90652APFV-G-195-BND absolute maximum ratings: (1)Power supply voltage, VCC1: VSS -0.3 to VSS + 4.0V; VCC2: VSS -0.3 to VSS +7.0 V; VCC(VCC1 = VCC2): VSS -0.3 to VSS +7.0 V ; (2)AVCC, VSS -0.3 to VSS + 4.0V; VSS -0.3 to VSS +7.0V ; (3)AVRH, AVRL: VSS -0.3 to VSS +4.0V; VSS -0.3 to VSS +7.0 V; DVRH, VSS -0.3 to VSS +4.0 V; VSS -0.3 V to VSS +7.0 V; (4)Input voltage, VI: VSS -0.3 to VSS +4.0 V; VSS -0.3 to VSS +7.0V; (5)Output voltage, VO: VSS -0.3 to VSS + 4.0V; VSS -0.3 to VSS +7.0V ; (6)“L” level maximum output current, IOL: 15 mA.

Features

MB90652APFV-G-195-BND features: (1)Minimum execution time: 62.5 ns/4 MHz oscillation (Uses PLL clock multiplication) maximum multiplier = 4; (2)Instruction set optimized for controller applications Object code compatibility with F2MC-16(H), Wide range of data types (bit, byte, word, and long word), Improved instruction cycles provide increased speed, Additional addressing modes: 23 modes; (3)High code efficiency, Access methods (bank access, linear pointer), High precision operations are enhanced by use of a 32-bit accumulator, Extended intelligent I/O service (access area extended to 64 Kbytes), Maximum memory space: 16 Mbytes; (4)Enhanced high level language (C) and multitasking support instructions, Use of a system stack pointer, Enhanced pointer indirect instructions Barrel shift instructions; (5)Improved execution speed: Four byte instruction queue; (6)Powerful interrupt function; (7)Automatic data transfer function that does not use instruction (extended I2OS).

Diagrams

(Hong Kong)

(Hong Kong)