Product Summary

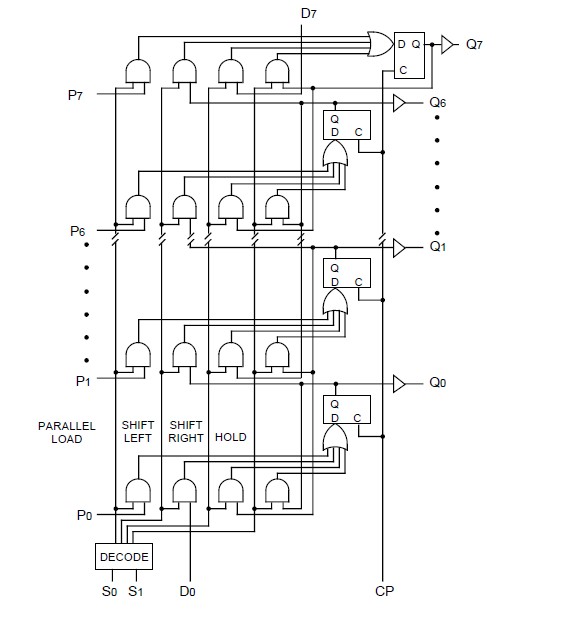

The SY100S341DC is an 8-bit shift register. The SY100S341DC offers eight D-type, edge-triggered flipflop with both individual inputs for parallel operation as well as serial inputs for bidirectional shifting, and are designed for use in high-performance ECL systems. Data is clocked into the flip-flops on the rising edge of the clock. The mode of operation is selected by two Select inputs (S0, S1) which determine if the SY100S341DC performs a shift, hold or parallel entry function, as described in the Truth Table. The inputs on the SY100S341DC has 75KΩ pull-down resistors.

Parametrics

SY100S341DC absolute maximum ratings: (1)IIH Input HIGH Current, All Inputs: 200 μA VIN = VIH (Max.); (2)IEE Power Supply Current : -150 to –71 mA; (3)fshift Shift Frequency: 600MHz.

Features

SY100S341DC features: (1)Max. shift frequency of 600MHz; (2)Max. Clock to Q delay of 1200ps; (3)IEE min. of –150mA; (4)Industry standard 100K ECL levels; (5)Extended supply voltage option: VEE = –4.2V to –5.5V; (6)Voltage and temperature compensation for improved noise immunity; (7)Internal 75KΩ input pull-down resistors; (8)70% faster than Fairchild 300K at lower power; (9)Function and pinout compatible with Fairchild F100K; (10)Available in 24-pin CERPACK and 28-pin PLCC packages.

Diagrams

(Hong Kong)

(Hong Kong)