Product Summary

The HY5DU283222AF-33 is a 134,217,728-bit CMOS Double Data Rate (DDR) Synchronous DRAM, ideally suited for the point-to-point applications which requires high bandwidth. The HY5DU283222AF-33 offers fully synchronous operations referenced to both rising and falling edges of the clock. All input and output voltage levels of the HY5DU283222AF-33 are compatible with SSTL_2.

Parametrics

HY5DU283222AF-33 absolute maximum ratings: (1) Ambient Temperature TA: 0 to 70°C; (2) Storage Temperature TSTG: -55 to 125°C; (3) Voltage on Any Pin relative to VSS, VIN, VOUT: -0.5 to 3.6V; (4) Voltage on VDD relative to VSS, VDD: -0.5 to 3.6V; (5) Voltage on VDDQ relative to VSS, VDDQ: -0.5 to 3.6V; (6) Output Short Circuit Current IOS: 50mA; (7) Power Dissipation PD: 2W; (8) Soldering Temperature .Time, TSOLDER: 260°C, 10 sec.

Features

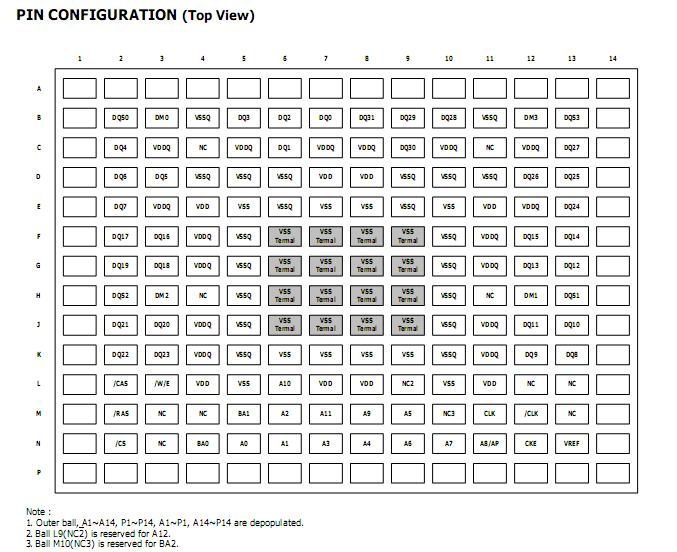

HY5DU283222AF-33 features: (1) 2.5V +/- 5% VDD and VDDQ power supply supports 300 / 275 / 250 / 200MHz; (2) 2.8V +/-5% VDD and VDDQ power supply supports 500/450/400/350MHz; (3) All inputs and outputs are compatible with SSTL_2 interface; (4) 12mm x 12mm, 144ball FBGA with 0.8mm pin pitch; (5) Fully differential clock inputs (CK, /CK) operation; (6) Internal 4 bank operations with single pulsed /RAS; (7) Auto refresh and self refresh supported; (8) Programmable Burst Length 2 / 4 / 8 with both sequential and interleave mode; (9) 4096 refresh cycles 32ms; (10) Half strength and Matched Impedance driver option controlled by EMRS.

Diagrams

(Hong Kong)

(Hong Kong)